Difference: Lecture10:DigitalToAnalogueConversion (3 vs. 4)

Revision 42017-11-03 - uli

| Line: 1 to 1 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||

| Changed: | |||||||||||||||

| < < | Digital to Analogue Conversion: the mcp4275Lecture 10 | ||||||||||||||

| > > |

Digital to Analogue Conversion:the mcp4275Lecture 10 | ||||||||||||||

Analogue versus digital | |||||||||||||||

| Line: 63 to 63 | |||||||||||||||

| |||||||||||||||

| Added: | |||||||||||||||

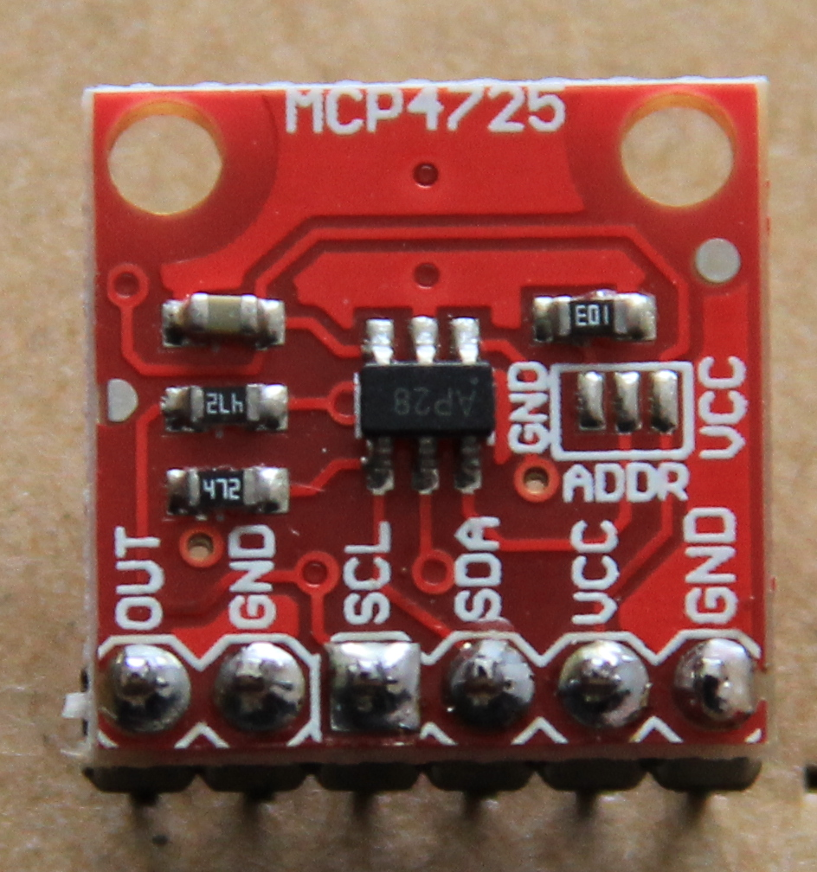

| > > | The I2C busThe I2C bus is an industrial standard 2 wire bus using a data (SDA) and a clock (SCL) line. Adding Vcc and Gnd we need a mere 4 wires to connect a I2C device to the Raspberry Pi cobbler The I2C bus was invented by PhilipsTypical I2C connections

Open drain signalsOpen drain signals mean that you can pull a line down but you cannot set it to a high level. If nobody pulls the line down, then it is at Vcc level, pulled up by a pull-up register. Like this the contention problem is solved where one device tries to set a line to a high level, while another sets it to low, thus creating a short circuit.I2C Master and slaveThe I2C bus has at least one master (in our case the interface in the Raspberry Pis ARM processor) and several slaves We have the following I2C slave devices:

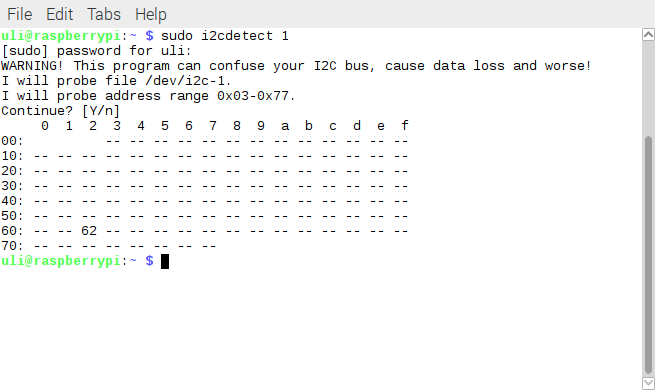

I2C addressingSince there can be several slaves on the bus there must be a means of distinguishing them through addressing: Every I2C slave has a 7 bit address associated with it Usually this address is determined by the manufacturer but often there are address pins on the devices allowing the user to have several devices of the same type on the busI2C buses and I2C addresses on the Raspberry PiThe Raspberry Pi has 2 I2C buses with bus 1 being put onto the cobbler You can find out the addresses of the I2C slaves are currently connected with the i2cdetect command

Initiating a I2C transfer

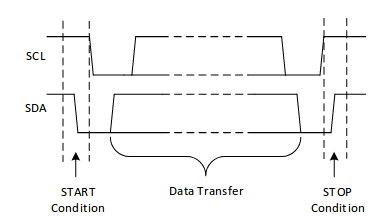

Start stop conditionsThe master starts a transfer by creating a start condition:

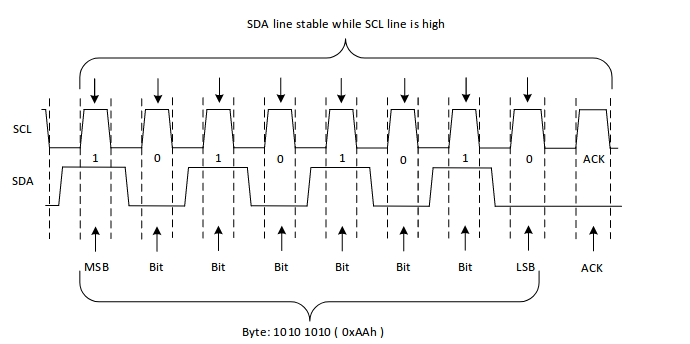

Data transmissionData are transmitted with the SDA line stable with SCL is high

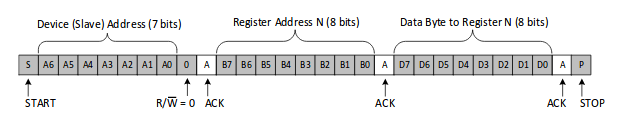

A write cycleA write cycle:After the start condition the device address. The eighth bit, the R/W bit is kept low. The second data byte is considered the register byte and the last one the data byte The slave acknowledges each byte transfer.

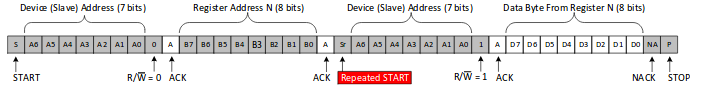

The read cycleThe read cycle is a bit more complex: First the master sends the slave address with R/W set to write Then it sends the register information. After that another address byte is sent, this time with RW set to read And finally the slave sends the data. The master still sends the clock but releases the SDA line allowing the slave to control it | ||||||||||||||

| %SLIDESHOWEND%

-- | |||||||||||||||

| Line: 86 to 210 | |||||||||||||||

| |||||||||||||||

| Added: | |||||||||||||||

| > > |

| ||||||||||||||

View topic | History: r6 < r5 < r4 < r3 | More topic actions...

Ideas, requests, problems regarding TWiki? Send feedback