| |

| META TOPICPARENT |

name="WebHome" |

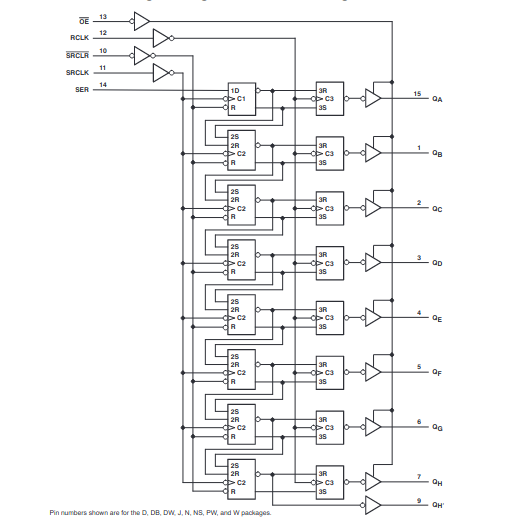

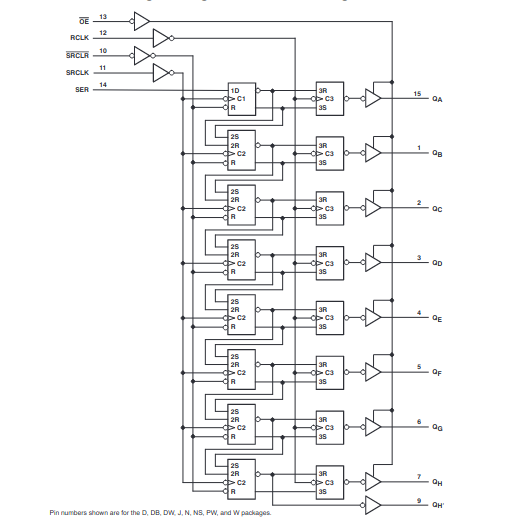

Le registre à décalage

Introduction |

| |

- SER: les données sérielles

- SRCLK: l'horloge pour les données. Sur le flanc montant de SRCLK le bit sur SER est transféré dans le registre à décalage

- SRCLR: Si le signale est mise à la masse tous les bits du registre à décalage sont effacé

|

|

<

< |

- RCLK: Sur le flanc montant de RCLK les données dans le registre à décalage sont transféré dans le de sortie

|

>

> |

- RCLK: Sur le flanc montant de RCLK les données dans le registre à décalage sont transféré dans le registre de sortie

|

| |

- OE: Si OE est à la masse le contenu du registre de sortie est visible sur les pins e sorti, autrement tous ces pins sont en haute impédance

|

| | Si on met

- OE à la masse (les pins de sortie sont toujours active)

- SCLR à Vcc

|

|

<

< |

- est on court-cicuit SRCLK et RCLK

alors seulement les lignes SER et SRCLK/RCLK doivent être contrôlé. |

>

> |

- et on court-circuite SRCLK et RCLK

alors le nombre de connexions à des pins GPIO peuvent être réduits à deux : SER et SRCLK |

| |

--  Uli Raich - 2021-06-20 Uli Raich - 2021-06-20 |