Le registre à décalage

Introduction

La barre à LEDs ou les afficheurs sept segments nécessitent beaucoup de pins GPIO si toutes leurs anodes ou cathodes sont connectés en parallèle. Puisque le nombre de pins GPIO disponible sur la carte CPU est limité il est intéressant de trouver une solution d'interfaçage avec moins de connexion. Un registre à décalage est un convertisseur série - parallèle qui prend des données bit par bit et les stocke dans un registre. Quand un bit est acquis, tous les bits pris précédemment sont décalé d'une position. La contenue du registre (8 bits en général) est disponible en parallèle.Le SN74HC595

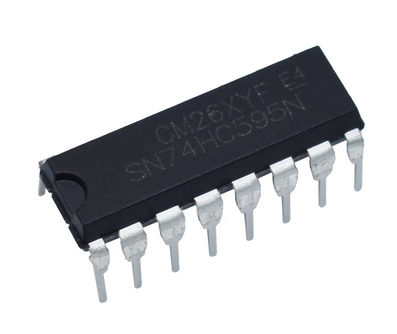

Le SN74HC595- le registre à décalage propre

- un registre de sortie

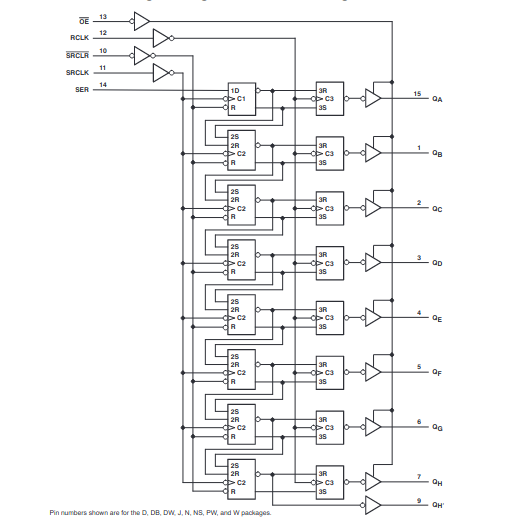

Comme on voit sur le diagramme bloque, 5 signaux de contrôle sont utilisés :

Comme on voit sur le diagramme bloque, 5 signaux de contrôle sont utilisés : - SER: les données sérielles

- SRCLK: l'horloge pour les données. Sur le flanc montant de SRCLK le bit sur SER est transféré dans le registre à décalage

- SRCLR: Si le signale est mise à la masse tous les bits du registre à décalage sont effacé

- RCLK: Sur le flanc montant de RCLK les données dans le registre à décalage sont transféré dans le registre de sortie

- OE: Si OE est à la masse le contenu du registre de sortie est visible sur les pins en sorti, autrement tous ces pins sont en haute impédance

Si on met

Si on met - OE à la masse (les pins de sortie sont toujours active)

- SCLR à Vcc

- et on court-circuite SRCLK et RCLK

Comments

| I | Attachment | History | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|---|

| |

74hc595.png | r1 | manage | 79.9 K | 2021-06-20 - 08:41 | UliRaich | |

| |

74hc595block.png | r1 | manage | 45.0 K | 2021-06-20 - 08:48 | UliRaich |

Ideas, requests, problems regarding TWiki? Send feedback